# **CST Schematic Supported Board File Formats**

**User Guide**

February 2018

Document Number: 052515-1.3

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2018, Intel Corporation. All rights reserved.

#### **Contents**

| 1 | SCT Supported Board File Formats | 5 |

|---|----------------------------------|---|

| 2 | Not Supported Board File Formats | 7 |

## **Revision History**

| Document<br>Number | Revision<br>Number | Description                                 | Revision Date |

|--------------------|--------------------|---------------------------------------------|---------------|

| 052515             | 1.0                | Initial release                             | May 2015      |

| 052515             | 1.2                | Document re- structure                      | Dec 2017      |

| 052515             | 1.3                | Updated Cadence and Mentor Graphics support | Jan 2018      |

| 052515             | 1.4                | Updated Mentor Graphics and Cadence formats | Feb 2018      |

| 052515             | 1.5                | Updated Cadence Software Names              | Feb 2018      |

## 1 SCT Supported Board File Formats

| EDA<br>Vendor      | ECAD SW                                                                     | SW version                 | Supported<br>File<br>Extension               | Notes                                                                        |

|--------------------|-----------------------------------------------------------------------------|----------------------------|----------------------------------------------|------------------------------------------------------------------------------|

| Cadence            | Allegro PCB Designer<br>(Allegro PCB Editor)                                | 16.6                       | .brd                                         | Component placement or trace routing not required                            |

|                    | Allegro Design Entry<br>CIS<br>(OrCAD Capture CIS)                          | 16.6 and 17.2              | .iscf                                        | iscf can be exported from a DSN.                                             |

|                    | Allegro Design Entry<br>HDL<br>(Concept HDL<br>Packaged Schematic<br>Files) | 16.6 and 17.2              | pstxref.dat,<br>pstchip.dat &<br>pstxprt.dat | .dat files are exported from DSN file                                        |

| Mentor<br>Graphics | Xpedition and VX.x.x                                                        | v2005<br>EE2007.x,<br>VX.x | .iscf                                        | .iscf can be exported from<br>DxDesigner                                     |

|                    | DxDesigner Schematic                                                        | v2005<br>EE2007.x,<br>VX.x | .iscf                                        | .iscf can be exported from<br>DxDesigner                                     |

|                    | PADS                                                                        |                            | .iscf                                        | .iscf can be exported from PADS                                              |

| Zuken              | CR-8000 Design<br>Gateway Schematic                                         | 2012.100<br>and later      | .iscf                                        | iscf can be exported directly from.<br>Design Gateway                        |

|                    | CR-5000 System<br>Designer Schematic                                        | 13.0 and later             | .iscf                                        | .iscf can be exported directly from<br>Design Gateway<br>(support.zuken.com) |

#### **Notes:**

- Please zip all files before uploading to your ticket.

- ISCF refers to Intel Schematic Checking Format, for instructions on how to export to .ISCF please contact CST.Services@intel.com.

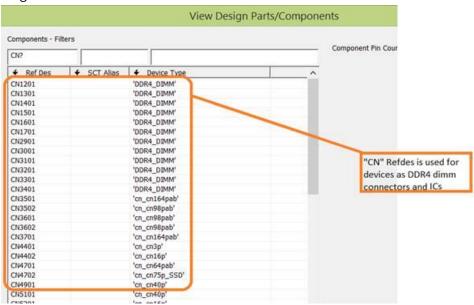

Schematic connector or ICs prefixes starting with "CN": Reference designators starting with "CN" are not allowed for automated schematic review. The automation always sees any component which name starts with "CN" as a 2-pin device regardless of the real pinout, causing false violations and graphic viewer captures. If your design has these condition we request to rename them before sending for review. For example, see the image below:

#### **Required Documents for Schematic Review:**

1. PDF Schematic

Complete and searchable

Preferable if it is non-hierarchical. If only hierarchical is available there might be a delay in completion

2. Board File or ISCF Extract (See table above)

Use to extract Netlists for automation

Component placement or trace routing not required

## 2 Not Supported Board File Formats

- Mentor Board Station.

- Altium Designer.

**Note:** This document does not in any way constitute an Intel endorsement of a product or supplier.

§